# System Design and Methodology/ Embedded Systems Design (Modeling and Design of Embedded Systems) TDTS07/TDD108

VT 2024

Soheil Samii

Institutionen för datavetenskap (IDA) Linköpings universitet

> email: <u>soheil.samii@liu.se</u> B building, 329:220

### **Course Information**

Web page: http://www.ida.liu.se/~TDTS07 http://www.ida.liu.se/~TDDI08

**Examination:** written, March 20, 14:00-18:00 labs (see course page and lesson notes)

Lecture notes: made available on the web page

Starting this semester, we are using Digital Exams in WISEflow:

- See instructions linked from our course web page (in the Examination section)

- Some preparation is needed ahead of the exam (downloading WISEflow, secure browser FLOWlock, test a demo flow, verify connection to Eduroam network)

- Bring your own laptop or book guest computer when registering for the exam

### **Course Information**

**Recommended literature:**

Peter Marwedel: "*Embedded System Design*", Springer, 2nd edition 2011, 3d edition 2018, 4th edition 2021.

The 4th edition is open access and available online via Springer.com

Edward Lee, Sanjit Seshia:"Introduction to Embedded Systems - A Cyber-Physical Systems Approach", 1st edition 2011, 2nd edition 2017 ' (available online: LeeSeshia.org)

### **Course Information**

Lessons&Labs:

Yungang Pan Institutionen för datavetenskap (IDA) email: <u>yungang.pan@liu.se</u> B building, 329:202

## **EMBEDDED SYSTEMS AND THEIR DESIGN**

- 1. What is an Embedded System

- 2. Characteristics of Embedded Applications

- 3. The Traditional Design Flow

- 4. An Example

- 5. A New Design Flow

- 6. The System Level

- 7. Course Topics

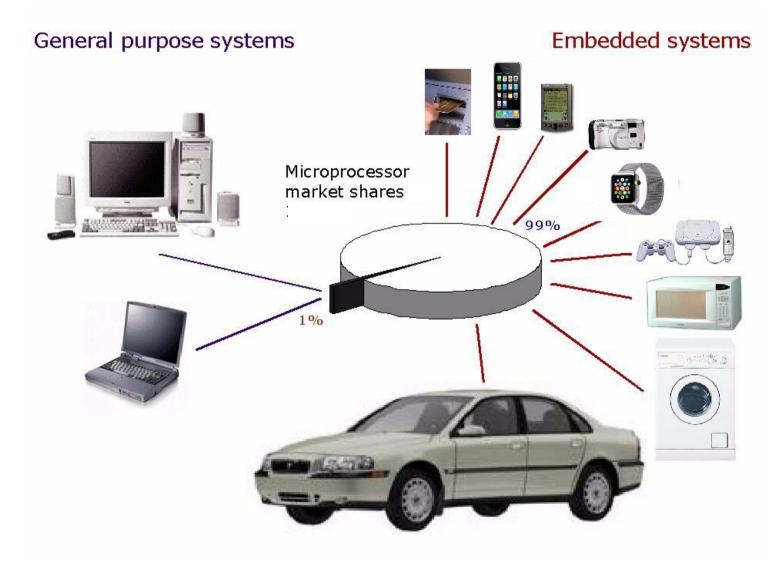

### That's how we use microprocessors

# What is an Embedded System?

There are several definitions around!

• Some highlight what it is (not) used for:

"An embedded system is any sort of device which includes a programmable component but itself is not intended to be a general purpose computer."

### What is an Embedded System?

There are several definitions around!

• Some highlight what it is (not) used for:

"An embedded system is any sort of device which includes a programmable component but itself is not intended to be a general purpose computer."

#### Some focus on what it is built from:

"An embedded system is a collection of programmable parts surrounded by ASICs and other standard components, that interact continuously with an environment through sensors and actuators."

### What is an Embedded System?

Some of the main characteristics:

- Dedicated (not general purpose)

- **Contains a programmable component**

- □ Interacts (continuously) with the environment

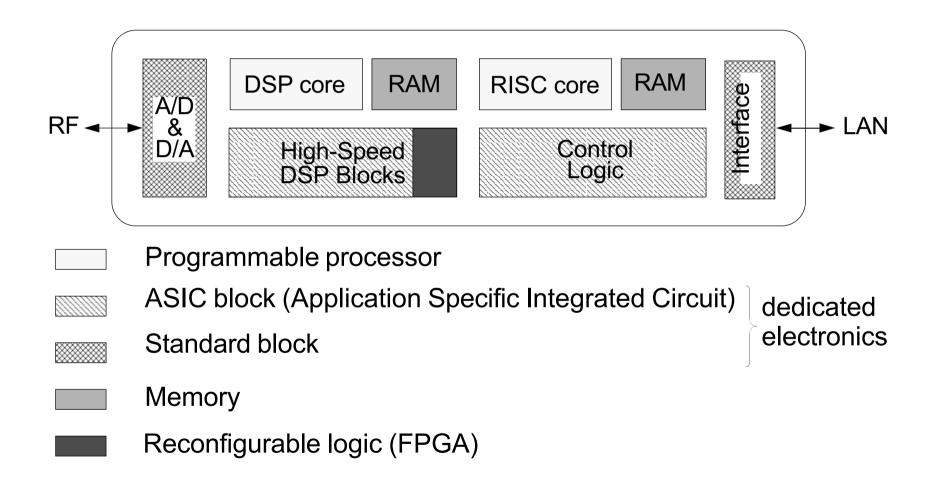

# **Two Typical Implementation Architectures**

### **Telecommunication System on Chip**

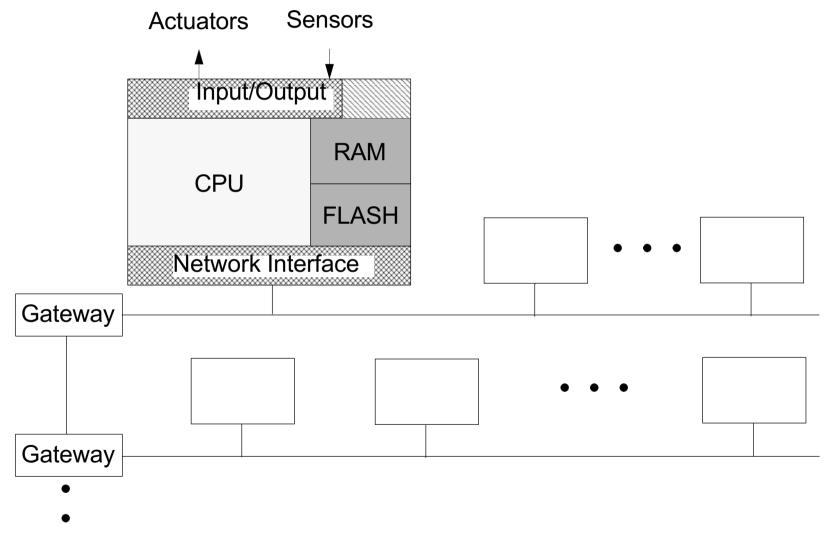

## **Two Typical Implementation Architectures**

#### **Distributed Embedded System (automotive application)**

•

## **The Software Component**

Software running on the programmable processors:

- **Application tasks**

- Real-Time Operating System

- □ I/O drivers, Network protocols, Middleware

## **Characteristics of Embedded Applications**

#### What makes them special?

Like with "ordinary" applications, functionality and user interfaces are often very complex.

### But, in addition to this:

- Time constraints

- **Power constraints**

- **Cost constraints**

- □ Safety

- **Time to market**

### **Time constraints**

- Embedded systems have to perform in real-time: if data is not ready by a certain deadline, the system fails to perform correctly.

- □ *Hard deadline*: failure to meet leads to major hazards.

- □ Soft deadline: failure to meet is tolerated but affects quality of service.

### **Power constraints**

• There are several reasons why low power/energy consumption is required:

#### □ Cost aspects:

High energy consumption ⇒ large electricity bill expensive power supply expensive cooling system

□ Reliability

High power consumption  $\Rightarrow$  high temperature that affects life time

#### **Battery life**

High energy consumption  $\Rightarrow$  short battery life time

**Environmental impact**

### **Cost constraints**

- Embedded systems are very often mass products in highly competitive markets and have to be shipped at a low cost.

- What we are interested in:

- □ Manufacturing cost

- **Design cost**

- □ Material cost (Bill of Material)

- □ Warranty cost

## Safety

- Embedded systems are often used in life critical applications: avionics, automotive electronics, nuclear plants, medical applications, military applications, etc.

- Reliability and safety are major requirements.

In order to guarantee safety during design:

- <u>Formal verification</u>: mathematics-based methods to verify certain properties of the designed system.

- <u>Automatic synthesis</u>:certain design steps are automatically performed by design tools.

### Short time to market

- In highly competitive markets it is critical to catch the market window: a short delay with the product on the market can have catastrophic financial consequences (even if the quality of the product is excellent).

- **Design time has to be reduced!**

- Good design methodologies.

- Efficient design tools.

- Reuse of previously designed and verified (hardw&softw) blocks.

- Good designers who understand both software and hardware!

## Why is Design of Embedded Systems Difficult?

- High Complexity

- □ Strong time&power constraints

- □ Low cost

- □ Short time to market

- Safety critical systems

In order to achieve these requirements, systems have to be highly optimized.

## Why is Design of Embedded Systems Difficult?

- High Complexity

- □ Strong time&power constraints

- □ Low cost

- □ Short time to market

- Safety critical systems

In order to achieve these requirements, systems have to be highly optimized.

Both hardware and software aspects have to be considered simultaneously!

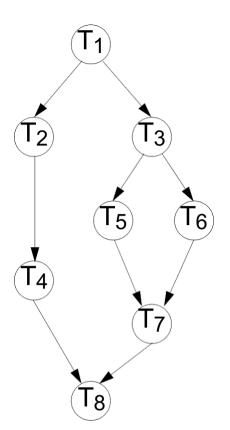

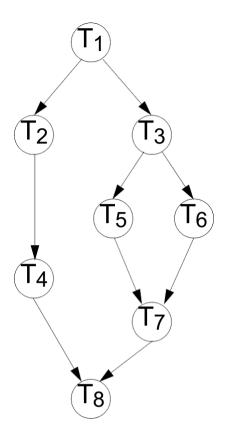

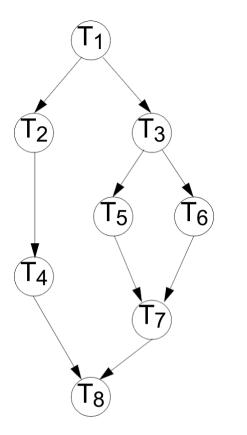

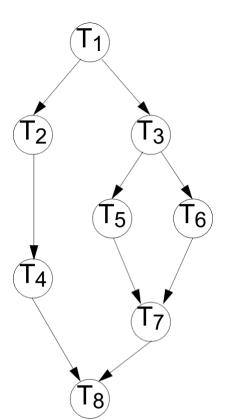

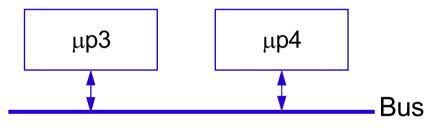

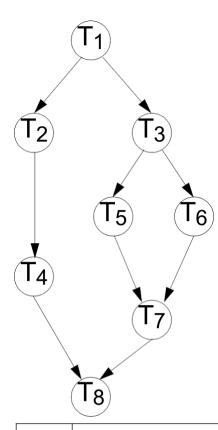

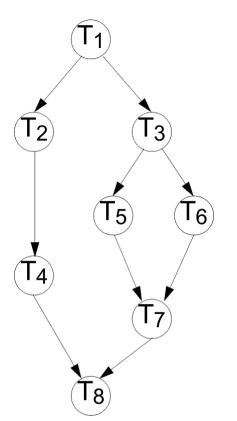

## **An Example**

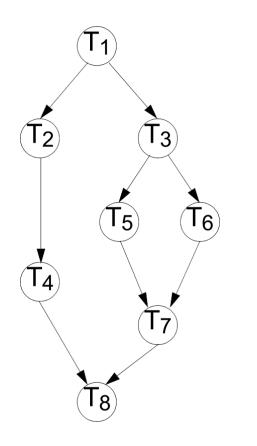

### The system to be implemented is modelled as a *task graph*:

- a node represents a *task* (a unit of functionality activated as response to a certain input and which generates a certain output).

- an edge represents a precedence constraint and data dependency between two tasks.

### Period: 42 time units

□ The task graph is activated every 42 time units  $\Rightarrow$  an activation has to terminate in time less than 42.

#### Cost limit: 8

The total cost of the implemented system has to be less than 8.

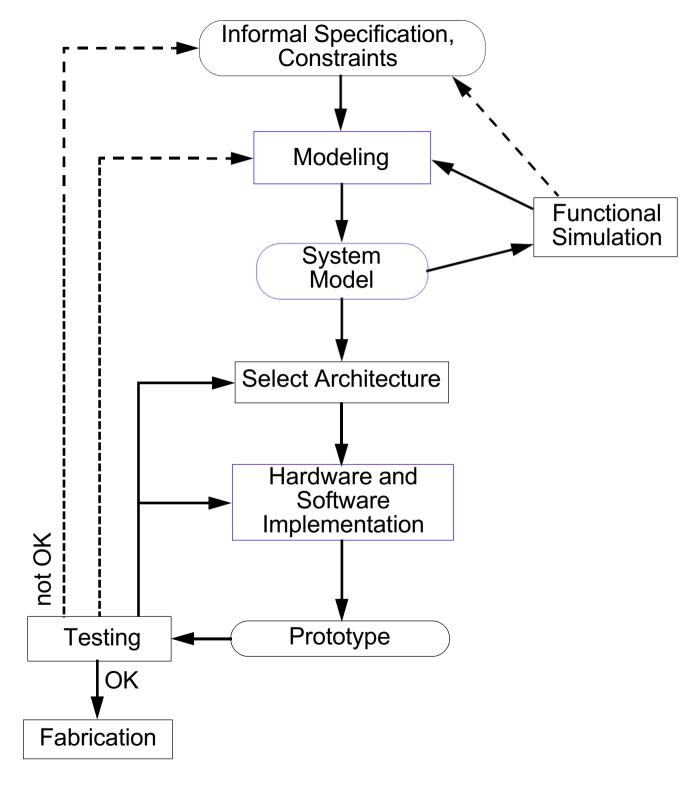

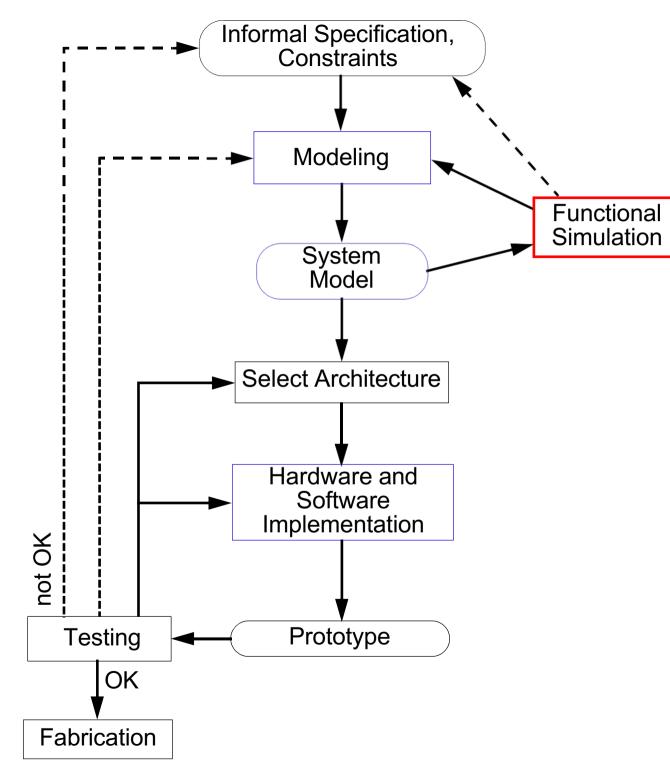

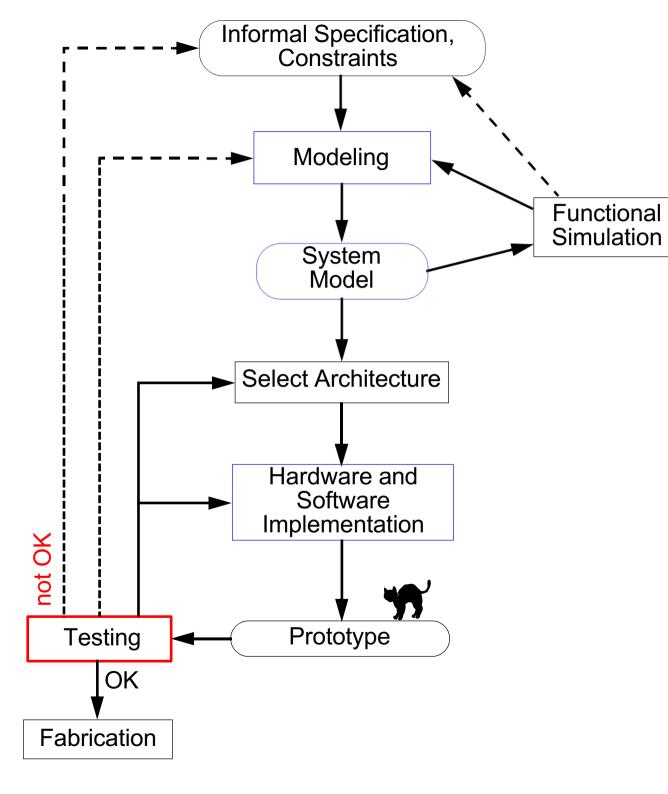

1. Start from some informal specification of functionality and a set of constraints

- 1. Start from some informal specification of functionality and a set of constraints

- 2. Generate a more formal model of the functionality, based on some modeling concept. Such model is our task graph

- 1. Start from some informal specification of functionality and a set of constraints

- 2. Generate a more formal model of the functionality, based on some modeling concept. Such model is our task graph

- 3. Simulate the model in order to check the functionality. If needed make adjustments.

- 1. Start from some informal specification of functionality and a set of constraints

- 2. Generate a more formal model of the functionality, based on some modeling concept. Such model is our task graph

- 3. Simulate the model in order to check the functionality. If needed make adjustments.

- 4. Choose an architecture (μprocessor, buses, etc.) such that cost limits are satisfied and, you hope, time and power constraints are fulfilled.

- 1. Start from some informal specification of functionality and a set of constraints

- 2. Generate a more formal model of the functionality, based on some modeling concept. Such model is our task graph

- 3. Simulate the model in order to check the functionality. If needed make adjustments.

- 4. Choose an architecture (μprocessor, buses, etc.) such that cost limits are satisfied and, you hope, time and power constraints are fulfilled.

- 5. Build a prototype and implement the system.

- 1. Start from some informal specification of functionality and a set of constraints

- 2. Generate a more formal model of the functionality, based on some modeling concept. Such model is our task graph

- 3. Simulate the model in order to check the functionality. If needed make adjustments.

- 4. Choose an architecture (μprocessor, buses, etc.) such that cost limits are satisfied and, you hope, time and power constraints are fulfilled.

- 5. Build a prototype and implement the system.

- 6. Verify the system: neither time nor power constraints are satisfied!!!

Now you are in great trouble: you have spent a lot of time and money and nothing works!

- Go back to 4, choose a new architecture and start a new implementation.

- Or negotiate with the customer on the constraints.

- The consequences:

- **Delays in the design process**

- Increased design cost

- Delays in time to market  $\Rightarrow$  missed market window

- □ High cost of failed prototypes

- **Bad design decisions taken under time pressure**

- Low quality, high cost products

1

T<sub>3</sub>)

$T_7$

5

8

16)

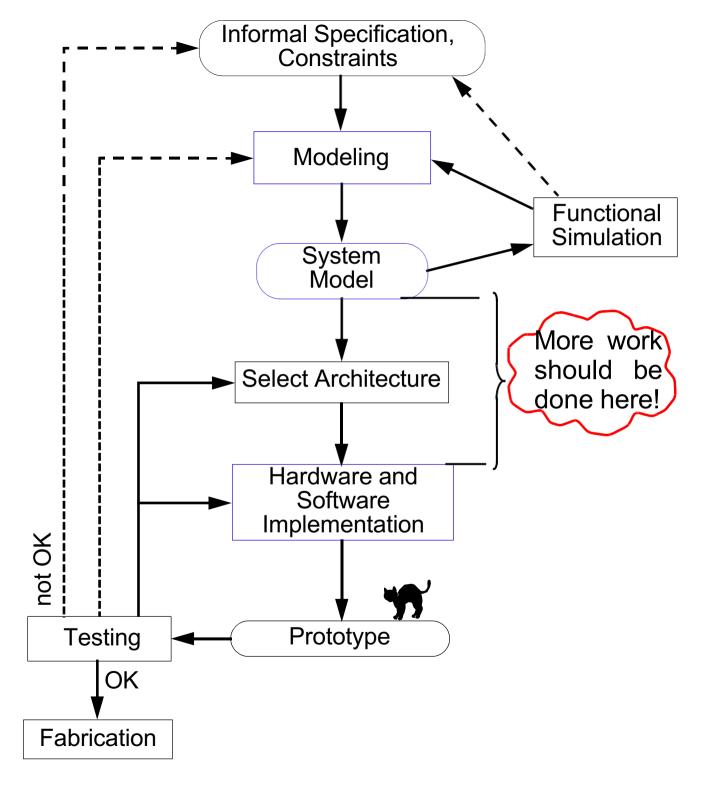

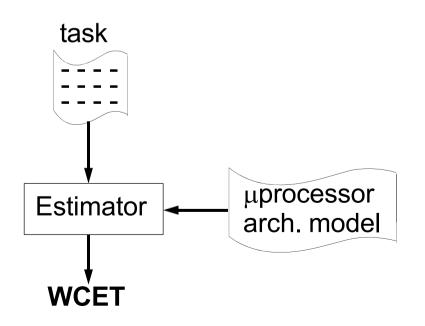

- We have the system model (task graph) which has been validated by simulation.

- We decide on a certain μprocessor μp1, with cost 6.

- For each task the worst case execution time (WCET) when run on μp1 is estimated.

1

15

8

4

Γ3)

$T_7$

16)

- We have the system model (task graph) which has been validated by simulation.

- **We decide on a certain** μ**processor** μ**p1, with cost 6.**

- For each task the worst case execution time (WCET) when run on μp1 is estimated.

1

15

**T**8

14

T<sub>3</sub>)

$T_7$

$\mathsf{T}_{6}$

- We have the system model (task graph) which has been validated by simulation.

- **We decide on a certain** μ**processor** μ**p1, with cost 6.**

- For each task the worst case execution time (WCET) when run on μp1 is estimated.

### We generate a schedule:

| Time | 0 2            | 4 6 8          | 10 12 14 16    | 18 20 | 22 24 26 28 | 30 32 34 36 38 40 | 42 44 46 4     | 8 50 52 54 56 58 | 60 62 64 |

|------|----------------|----------------|----------------|-------|-------------|-------------------|----------------|------------------|----------|

|      | T <sub>1</sub> | T <sub>2</sub> | T <sub>4</sub> | T3    | T5          | T <sub>6</sub>    | T <sub>7</sub> | T <sub>8</sub>   |          |

| Task           | WCET |

|----------------|------|

| T <sub>1</sub> | 4    |

| T <sub>2</sub> | 6    |

| T <sub>3</sub> | 4    |

| T4             | 7    |

| T5             | 8    |

| T <sub>6</sub> | 12   |

| T <sub>7</sub> | 7    |

| T <sub>8</sub> | 10   |

### We generate a schedule:

Time

0

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

T1

T2

T4

T3

T5

T6

T7

T8

Using the architecture with  $\mu$ processor  $\mu$ p1 we got a solution with:

- □ Cost: 6 < 8

We have to try with another architecture!

| Task           | WCET |

|----------------|------|

| T1             | 4    |

| T <sub>2</sub> | 6    |

| T3             | 4    |

| T4             | 7    |

| T5             | 8    |

| T <sub>6</sub> | 12   |

| T7             | 7    |

| T <sub>8</sub> | 10   |

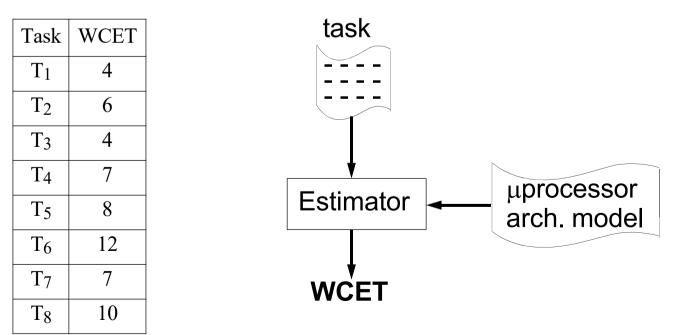

We look after a  $\mu \text{processor}$  which is fast enough:  $\mu \text{p2}$

#### Task WCET $T_1$ 2 3 $T_2$ 2 T3 T4 3 T5 4 $T_6$ 6 $T_7$ 3 5 $T_8$

## Example

We look after a  $\mu\text{processor}$  which is fast enough:  $\mu\text{p2}$

For each task the WCET, when run on  $\mu$ p2, is estimated.

We look after a  $\mu\text{processor}$  which is fast enough:  $\mu\text{p2}$

For each task the WCET, when run on  $\mu$ p2, is estimated.

Using the architecture with  $\mu$ processor  $\mu$ p2, after generating a schedule, we got a solution with:

□ Execution time: 28 < 42

WCET Task  $T_1$ 2 3  $T_2$ Т٦ 2 3 T<sub>4</sub> T5 4 T<sub>6</sub> 6  $T_7$ 3 5  $T_8$

18

1

15

[3]

**Г**7`

$\mathsf{T}_6$

We have to try with another architecture!

1

$\mathsf{T}_5$

T8

14

Гз

$\Gamma_7$

$\widehat{\mathsf{T}_6}$

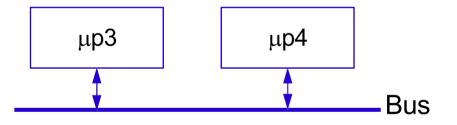

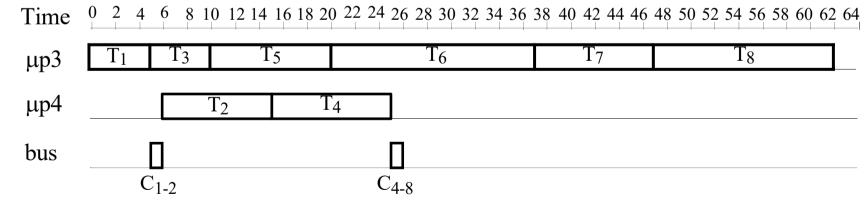

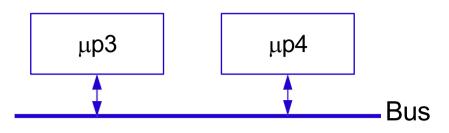

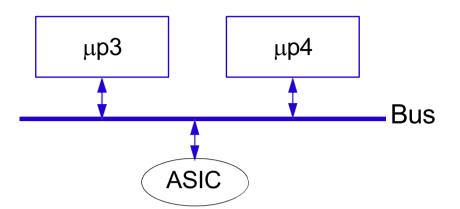

We have to look for a multiprocessor solution

In order to meet cost constraints try 2 cheap (and slow) μps:

μp3: cost 3

μp4: cost 2

interconnection bus: cost 1

We have to look for a multiprocessor solution

In order to meet cost constraints try 2 cheap (and slow) μps: μp3: cost 3 μp4: cost 2 interconnection bus: cost 1

For each task the WCET, when run on  $\mu$ p3 and  $\mu$ p4, is estimated.

| Task           | WCET |     |  |  |  |

|----------------|------|-----|--|--|--|

| 1 ask          | μр3  | μp4 |  |  |  |

| T <sub>1</sub> | 5    | 6   |  |  |  |

| T <sub>2</sub> | 7    | 9   |  |  |  |

| T3             | 5    | 6   |  |  |  |

| T4             | 8    | 10  |  |  |  |

| T5             | 10   | 11  |  |  |  |

| T <sub>6</sub> | 17   | 21  |  |  |  |

| T <sub>7</sub> | 10   | 14  |  |  |  |

| T8             | 15   | 19  |  |  |  |

ြဒ

7

15

| 4

$T_6$

#### 41 of 63

$T_2$   $T_3$   $T_5$   $T_6$   $T_7$   $T_7$   $T_8$

1

| Task           | WCET |     |  |

|----------------|------|-----|--|

| 1 ask          | μр3  | μp4 |  |

| T <sub>1</sub> | 5    | 6   |  |

| T <sub>2</sub> | 7    | 9   |  |

| T3             | 5    | 6   |  |

| T4             | 8    | 10  |  |

| T5             | 10   | 11  |  |

| T <sub>6</sub> | 17   | 21  |  |

| T <sub>7</sub> | 10   | 14  |  |

| T <sub>8</sub> | 15   | 19  |  |

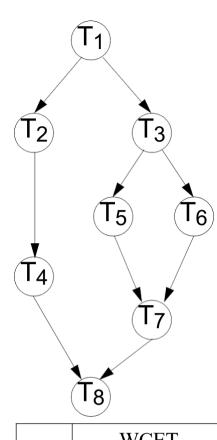

Now we have to map the tasks to processors:  $\mu$ p3: T<sub>1</sub>, T<sub>3</sub>, T<sub>5</sub>, T<sub>6</sub>, T<sub>7</sub>, T<sub>8</sub>.  $\mu$ p4: T<sub>2</sub>, T<sub>4</sub>.

If communicating tasks are mapped to different processors, they have to communicate over the bus.

Communication time has to be estimated; it depends on the amount of bits transferred between the tasks and on the speed of the bus.

**Estimated communication times**:

- C<sub>1-2</sub>: 1

- C<sub>4-8</sub>: 1

μ**p3: T<sub>1</sub>, T<sub>3</sub>, T<sub>5</sub>, T<sub>6</sub>, T<sub>7</sub>, T<sub>8</sub>.** μ**p4: T<sub>2</sub>, T<sub>4</sub>.**

Estimated communication times: C<sub>1-2</sub>: 1 C<sub>4-8</sub>: 1

#### We generate a schedule:

| Task           | WC  | CE I | Time   | 0 2 4 6        |

|----------------|-----|------|--------|----------------|

| 1 ask          | μp3 | μp4  | 1 1110 |                |

| T <sub>1</sub> | 5   | 6    | μp3    | T <sub>1</sub> |

| T <sub>2</sub> | 7   | 9    | μp4    | [              |

| T3             | 5   | 6    | bus    | п              |

| T4             | 8   | 10   |        | <b>L</b>       |

| T5             | 10  | 11   |        | _              |

| T <sub>6</sub> | 17  | 21   |        |                |

| T <sub>7</sub> | 10  | 14   |        |                |

| T <sub>8</sub> | 15  | 19   |        |                |

|                |     |      |        |                |

μ**p3: T<sub>1</sub>, T<sub>3</sub>, T<sub>5</sub>, T<sub>6</sub>, T<sub>7</sub>, T<sub>8</sub>.** μ**p4: T<sub>2</sub>, T<sub>4</sub>.**

Estimated communication times: C<sub>1-2</sub>: 1 C<sub>4-8</sub>: 1

#### We generate a schedule:

We have exceeded the allowed execution time (42)!

| Taalr          | WCET |     |  |

|----------------|------|-----|--|

| Task           | μp3  | μp4 |  |

| T <sub>1</sub> | 5    | 6   |  |

| T <sub>2</sub> | 7    | 9   |  |

| T3             | 5    | 6   |  |

| T4             | 8    | 10  |  |

| T5             | 10   | 11  |  |

| T <sub>6</sub> | 17   | 21  |  |

| T <sub>7</sub> | 10   | 14  |  |

| T8             | 15   | 19  |  |

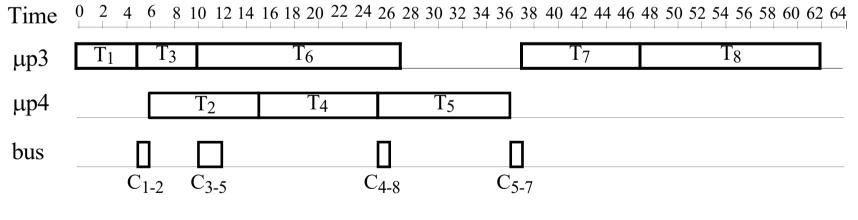

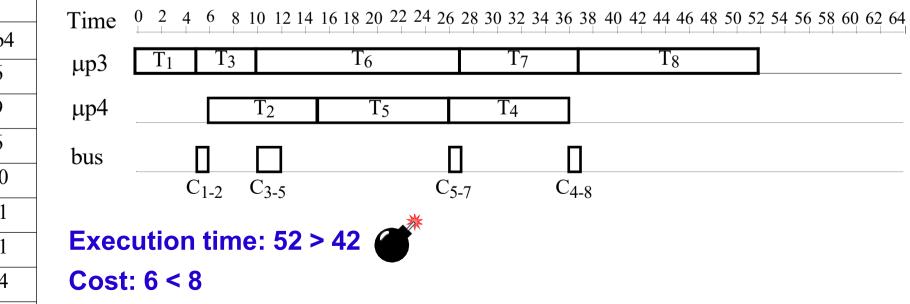

Try a new mapping; T<sub>5</sub> to  $\mu$ p4, in order to increase parallelism. Two new communications are introduced, with estimated times: C<sub>3-5</sub>: 2 C<sub>5-7</sub>: 1

#### We generate a schedule:

The execution time is still 62, as before!

| Taalr          | WCET |     |  |  |

|----------------|------|-----|--|--|

| Task -         | μр3  | μp4 |  |  |

| T <sub>1</sub> | 5    | 6   |  |  |

| T <sub>2</sub> | 7    | 9   |  |  |

| T3             | 5    | 6   |  |  |

| T4             | 8    | 10  |  |  |

| T5             | 10   | 11  |  |  |

| T <sub>6</sub> | 17   | 21  |  |  |

| T <sub>7</sub> | 10   | 14  |  |  |

| T <sub>8</sub> | 15   | 19  |  |  |

1

15

18

Ι Δ

ြဒ

$T_6$

Try a new mapping;  $T_5$  to  $\mu$ p4, in order to increase parallelism. Two new communications are introduced, with estimated times: C<sub>3-5</sub>: 2 C<sub>5-7</sub>: 1

#### There exists a better schedule!

11

$\mathsf{T}_5$

T<sub>8</sub>

μр3

5

7

5

8

10

17

10

15

Τ4

Task

$T_1$

$T_2$

T3

T<sub>4</sub>

T<sub>5</sub>

T<sub>6</sub>

$T_7$

$T_8$

T<sub>3</sub>

$T_7$

WCET

11

21

14

19

$\widehat{\mathsf{T}_6}$

| 21       | Time | 0 2 4 6 8 10 12 14                | 16 18 20 22 24 2 | 26 28 30 32 34 36 38 | 8 40 42 44 46 48 50 52 | 54 56 58 60 62 64 |

|----------|------|-----------------------------------|------------------|----------------------|------------------------|-------------------|

| μp4<br>6 | μp3  | T <sub>1</sub> T <sub>3</sub>     | T <sub>6</sub>   | T <sub>7</sub>       | T <sub>8</sub>         |                   |

| 9        | μp4  | T <sub>2</sub>                    | T5               | Τ4                   |                        |                   |

| 6        | bus  |                                   |                  | п п                  |                        |                   |

| 10       |      | C <sub>1-2</sub> C <sub>3-5</sub> | (                | $C_{5-7}$ $C_{4-8}$  |                        |                   |

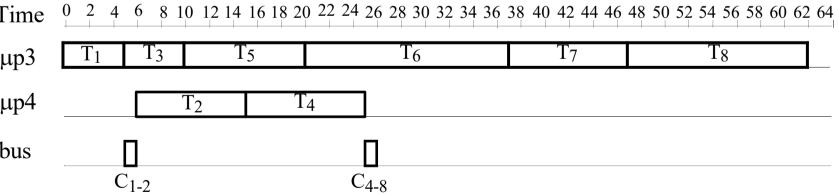

Try a new mapping; T<sub>5</sub> to  $\mu$ p4, in order to increase parallelism. Two new communications are introduced, with estimated times: C<sub>3-5</sub>: 2 C<sub>5-7</sub>: 1

#### There exists a better schedule!

WCET Task μр3 μp4  $T_1$ 5 6  $T_2$ 7 9 T3 5 6 T4 8 10 T5 10 11 T<sub>6</sub> 17 21  $T_7$ 10 14 **T**8 15 19

1

$\mathsf{T}_5$

T8

4

Гз

$T_7$

$T_6$

Possible solutions:

$\square$  Change  $\mu \text{proc.}\ \mu \text{p3}$  with faster one  $\Rightarrow$  cost limits exceeded

| Task           | WCET |     |  |

|----------------|------|-----|--|

| Task           | μр3  | μp4 |  |

| T <sub>1</sub> | 5    | 6   |  |

| T <sub>2</sub> | 7    | 9   |  |

| T3             | 5    | 6   |  |

| T4             | 8    | 10  |  |

| T5             | 10   | 11  |  |

| T <sub>6</sub> | 17   | 21  |  |

| T <sub>7</sub> | 10   | 14  |  |

| T <sub>8</sub> | 15   | 19  |  |

#### 48 of 63

| Examp | le |

|-------|----|

|       |    |

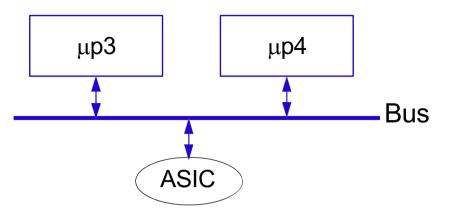

Possible solutions:

$\square$  Change  $\mu \text{proc.}\ \mu \text{p3}$  with faster one  $\Rightarrow$  cost limits exceed

Implement part of the functionality in hardware as an ASIC

Cost of ASIC: 1

| Task           | WCET |     |  |  |

|----------------|------|-----|--|--|

| Task           | μр3  | μp4 |  |  |

| T <sub>1</sub> | 5    | 6   |  |  |

| T <sub>2</sub> | 7    | 9   |  |  |

| T3             | 5    | 6   |  |  |

| T4             | 8    | 10  |  |  |

| T5             | 10   | 11  |  |  |

| T <sub>6</sub> | 17   | 21  |  |  |

| T <sub>7</sub> | 10   | 14  |  |  |

| T <sub>8</sub> | 15   | 19  |  |  |

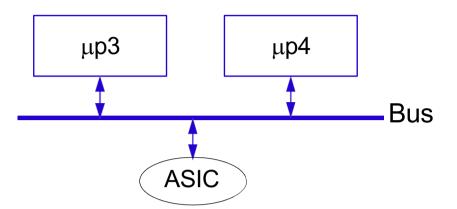

□ Change µproc. µp3 with faster one  $\Rightarrow$  cost limits exceed □ Implement part of the functionality in hardware as an ASIC

New architecture

Cost of ASIC: 1

Mapping

μp3: T<sub>1</sub>, T<sub>3</sub>, T<sub>6</sub>, T<sub>7</sub>.

μ**p4: T<sub>2</sub>, T<sub>4</sub>, T<sub>5</sub>.**

- ASIC: T<sub>8</sub> with estimated WCET= 3

- New communication, with estimated time:

C<sub>7-8</sub>: 1

| (              | <b>T</b> 8 |     |  |

|----------------|------------|-----|--|

| Task           | WCET       |     |  |

| 1 ask          | μр3        | μp4 |  |

| T <sub>1</sub> | 5          | 6   |  |

| T <sub>2</sub> | 7          | 9   |  |

| T3             | 5          | 6   |  |

| T <sub>4</sub> | 8          | 10  |  |

| T5             | 10         | 11  |  |

| T <sub>6</sub> | 17         | 21  |  |

| T <sub>7</sub> | 10         | 14  |  |

| T8             | 15         | 19  |  |

1

15

4

3

Γ<sub>7</sub>`

$T_6$

- Mapping

μp3: T<sub>1</sub>, T

- 18 WCET Task μр3 μp4  $T_1$ 5 6 ----- $T_2$ 7 9 T3 5 6 T<sub>4</sub> 8 10 T5 10 11 T<sub>6</sub> 17 21  $T_7$ 10 14  $T_8$ 15 19

1

Τ5

14

Гз

Γ7

$T_6$

- μp3: T<sub>1</sub>, T<sub>3</sub>, T<sub>6</sub>, T<sub>7</sub>. μp4: T<sub>2</sub>, T<sub>4</sub>, T<sub>5</sub>. ASIC: T<sub>8</sub> with estimated WCET= 3

- New communication, with estimated time: C<sub>7-8</sub>: 1

| Гime | 0 2 4          | 6 8              | 3 10 12 14       | 4 16 18 20 22  | 24 26 28 30      | 32 34 36 38        | 40 42 4        | 4 46 48 50 | 0 52 54 56 | 58 60 62 64 |

|------|----------------|------------------|------------------|----------------|------------------|--------------------|----------------|------------|------------|-------------|

| μрЗ  | T <sub>1</sub> | T3               |                  | T <sub>6</sub> |                  | T <sub>7</sub>     |                |            |            |             |

| µp4  |                |                  | T <sub>2</sub>   | T5             | ] ]              | 4                  |                |            |            |             |

| ASIC |                |                  |                  |                |                  |                    | T <sub>8</sub> |            |            |             |

| bus  |                |                  |                  |                |                  | Ш                  |                |            |            |             |

|      | (              | C <sub>1-2</sub> | C <sub>3-5</sub> |                | C <sub>5-7</sub> | C <sub>4-8</sub> C | 7-8            |            |            | 51 of 63    |

# T<sub>3</sub>

$\widehat{\mathsf{T}_6}$

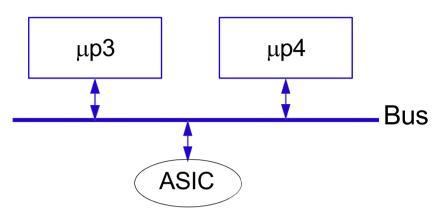

Example

Using this architecture we got a solution with:

□ Execution time: 41 < 42

□ Cost: 7 < 8

| Task           | WC  | CET |

|----------------|-----|-----|

| TASK           | μp3 | μp4 |

| T <sub>1</sub> | 5   | 6   |

| T <sub>2</sub> | 7   | 9   |

| T3             | 5   | 6   |

| T4             | 8   | 10  |

| T5             | 10  | 11  |

| T <sub>6</sub> | 17  | 21  |

| T <sub>7</sub> | 10  | 14  |

| T <sub>8</sub> | 15  | 19  |

1

T5

8

ſ<sub>7</sub>`

14

| Time |                | 6 8 1       | 0 12 14          | 16 18 20 2 | 22 24 26       | 5 28 30 3 | 2 34 36   | 5 38 40   | 42 44 | 464 | 8 50 | 52 54 | 56 58 | 8 60    | 62 64 |

|------|----------------|-------------|------------------|------------|----------------|-----------|-----------|-----------|-------|-----|------|-------|-------|---------|-------|

| μрЗ  | T <sub>1</sub> | T3          |                  | T6         | T              | 7         |           |           |       |     |      |       |       |         |       |

| μp4  |                |             | T <sub>2</sub>   | T5         |                | T4        |           |           |       |     |      |       |       |         |       |

| ASIC |                |             |                  |            |                |           |           | T8        |       |     |      |       |       |         |       |

| bus  |                |             |                  |            | [              | ]         | [         | П         |       |     |      |       |       |         |       |

|      | (              | $C_{1-2}$ ( | C <sub>3-5</sub> |            | C <sub>4</sub> | 5-7       | $C_{4-8}$ | $C_{7-8}$ |       |     |      |       | 5     | 52 of 6 | 53    |

#### What did we achieve?

- **We have selected an architecture.**

- □ We have mapped tasks to the processors and ASIC.

- □ We have elaborated a a schedule.

#### What did we achieve?

- □ We have selected an architecture.

- □ We have mapped tasks to the processors and ASIC.

- □ We have elaborated a a schedule.

**Extremely important!!!**

Nothing has been built yet.

All decisions are based on simulation and estimation.

#### What did we achieve?

- □ We have selected an architecture.

- □ We have mapped tasks to the processors and ASIC.

- □ We have elaborated a a schedule.

Extremely important!!!

Nothing has been built yet.

All decisions are based on simulation and estimation.

Now we can go and do the software and hardware implementation, with a high degree of confidence that we get a correct prototype.

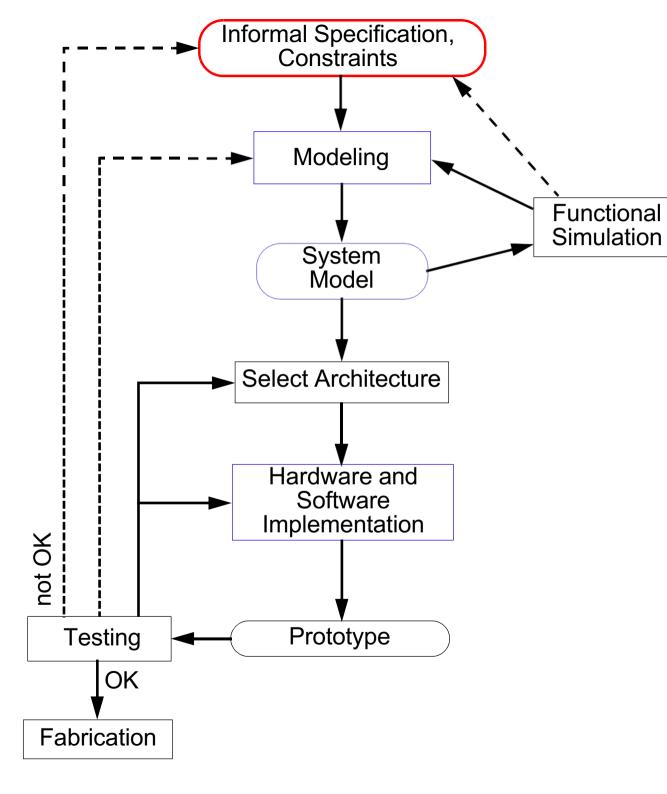

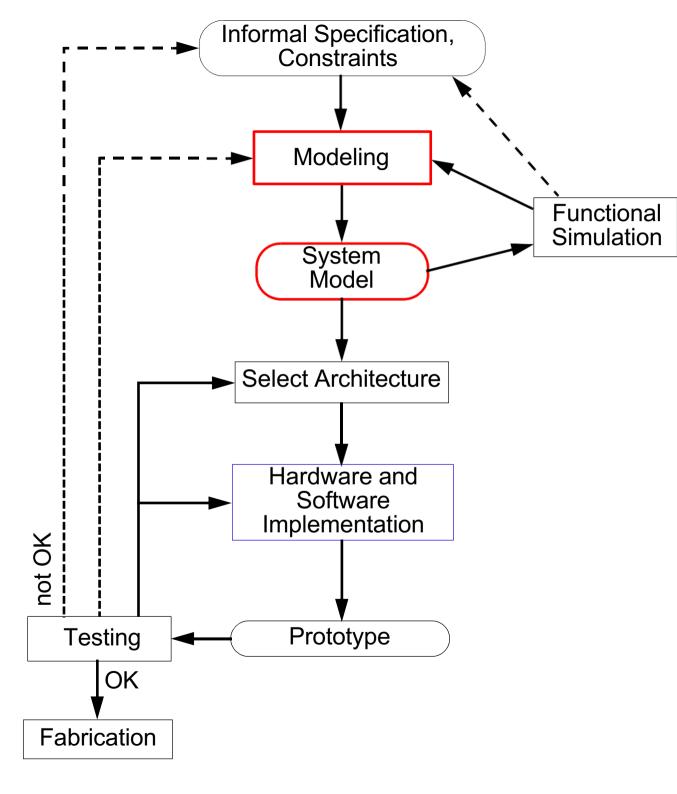

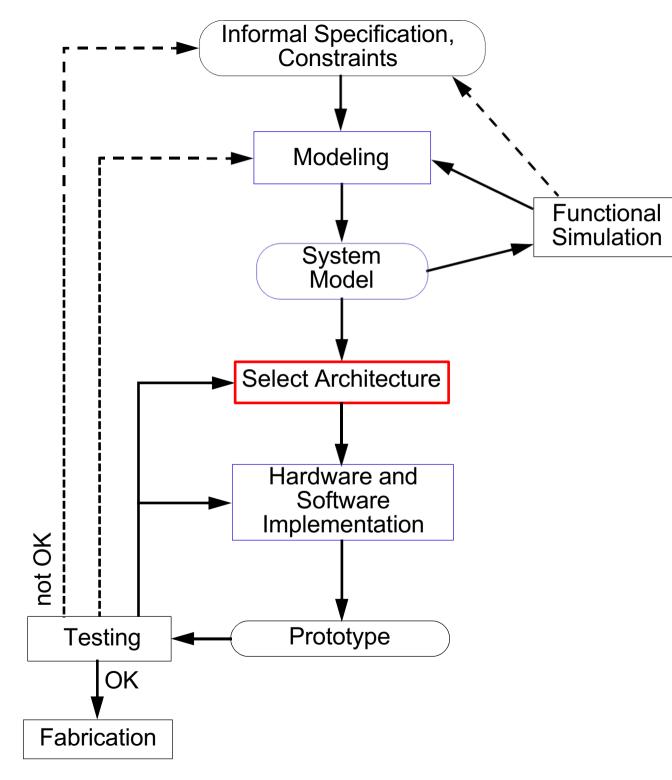

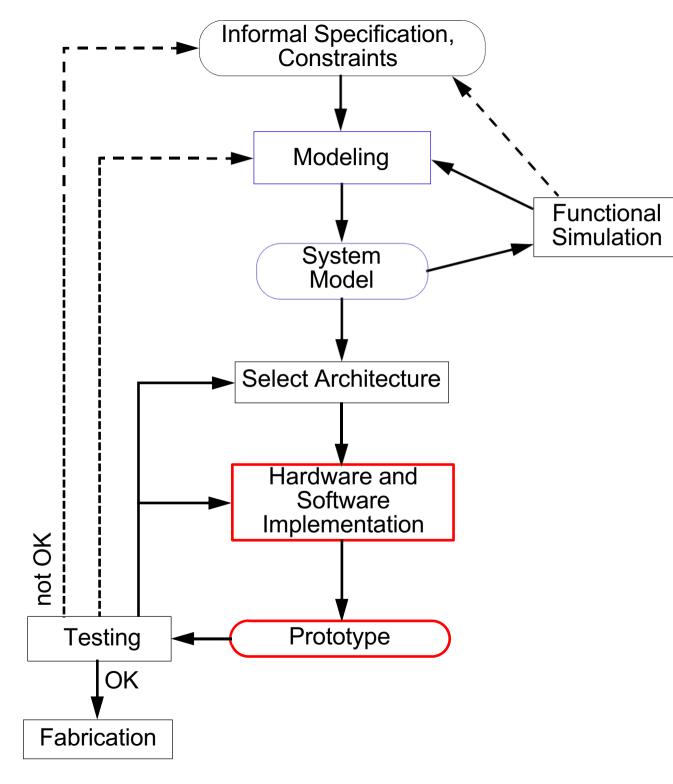

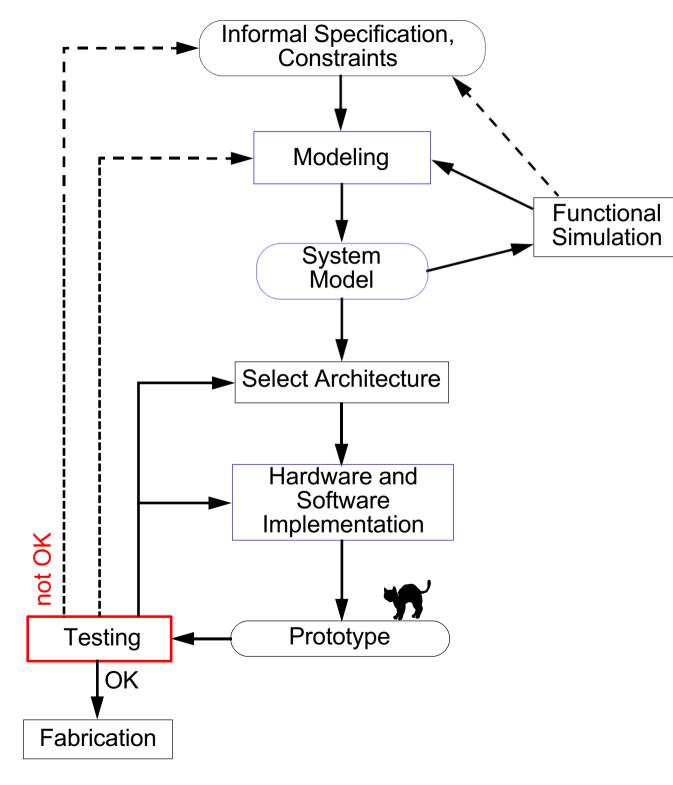

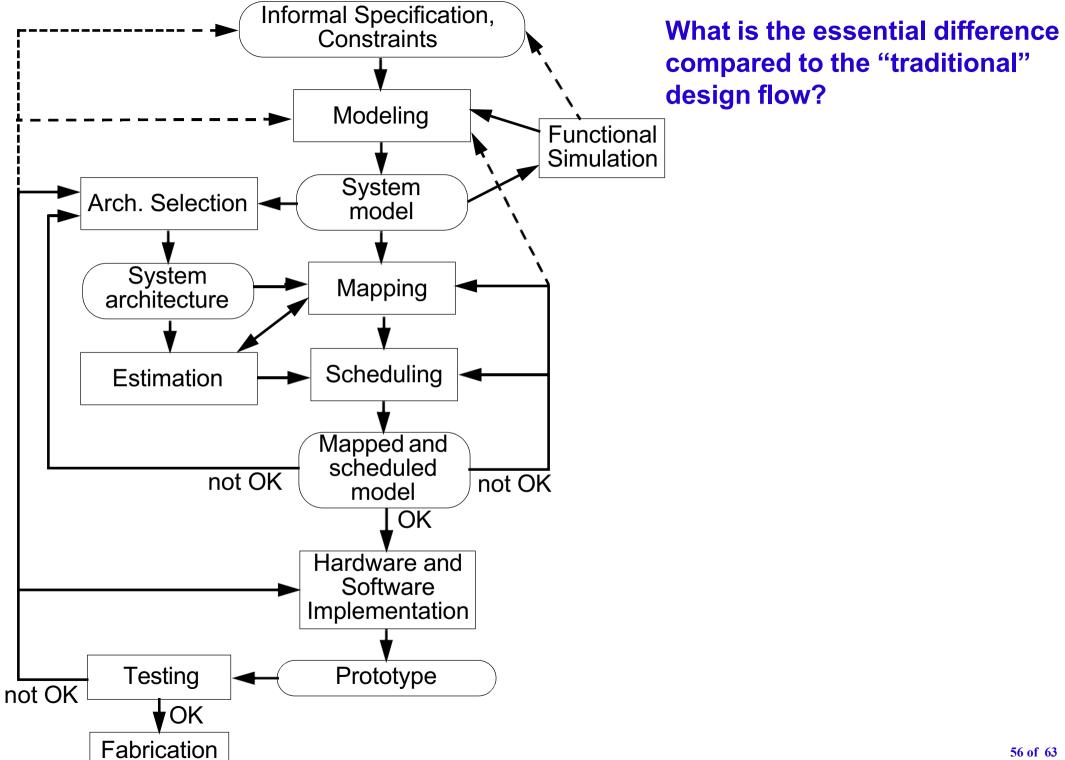

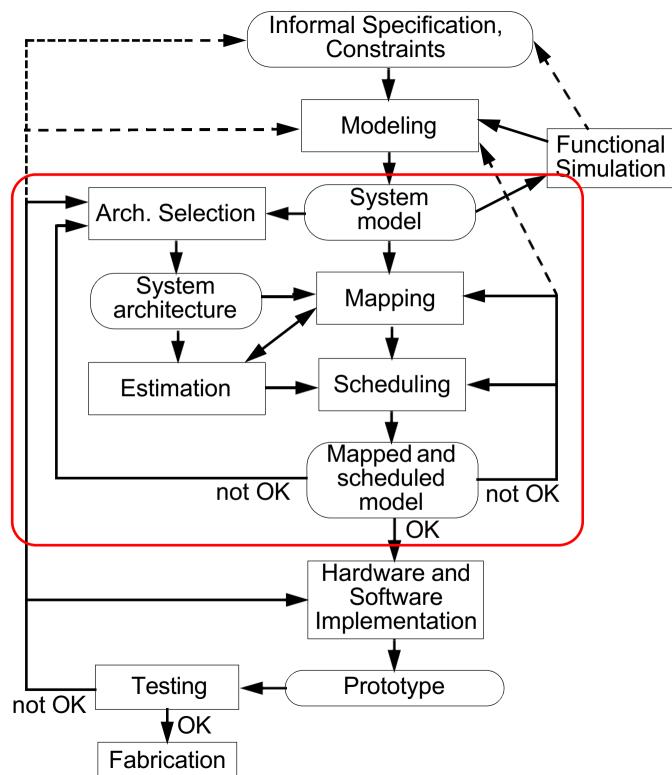

What is the essential difference compared to the "traditional" design flow?

The inner loop which is performed before the hardware/ software implementation.

This loop is performed several times as part of the <u>design</u> <u>space exploration</u>. Different architectures, mappings and schedules are explored, <u>be-</u> fore the actual implementation and prototyping.

We get highly optimized good quality solutions in short time.

We have a good chance that the outer loop, including prototyping, is not repeated.

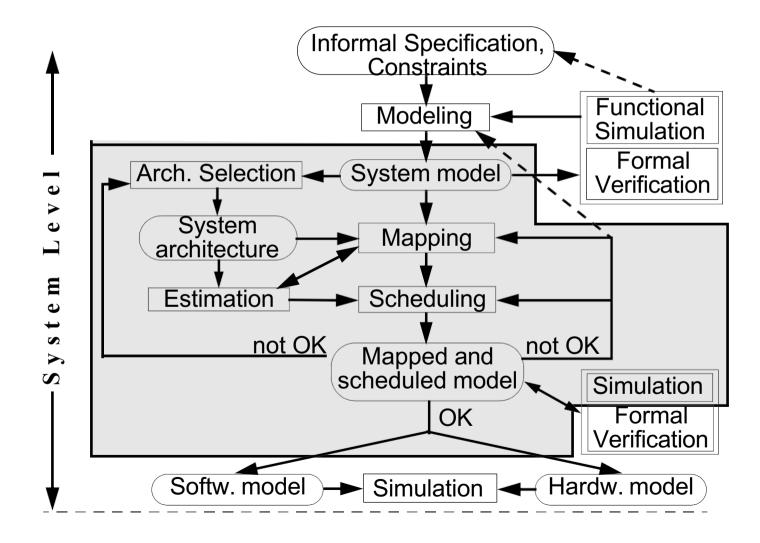

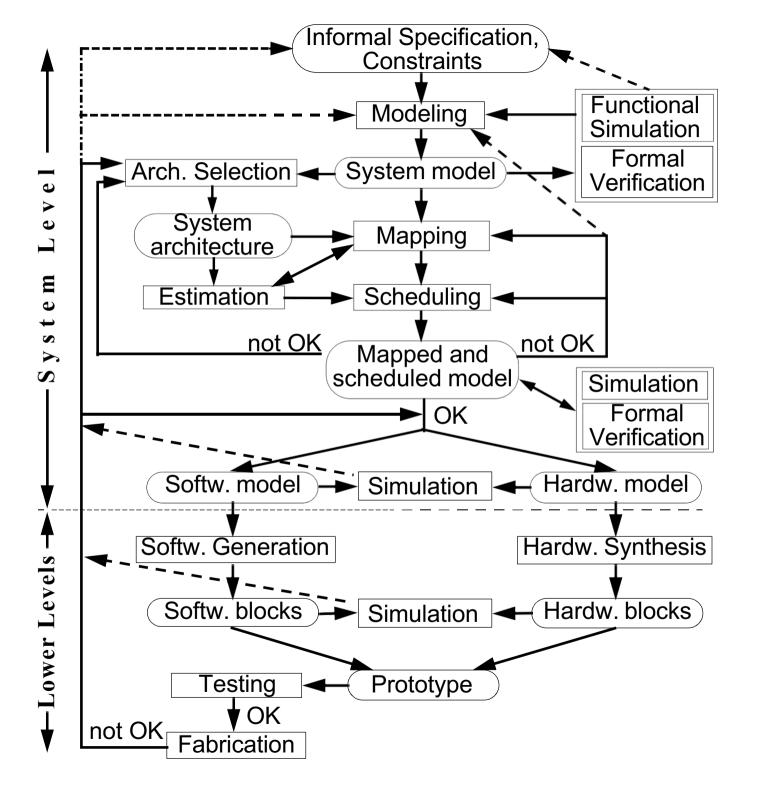

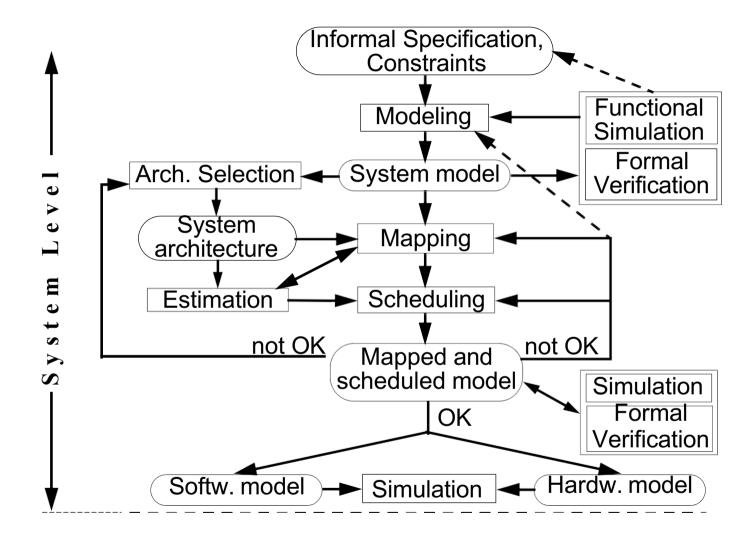

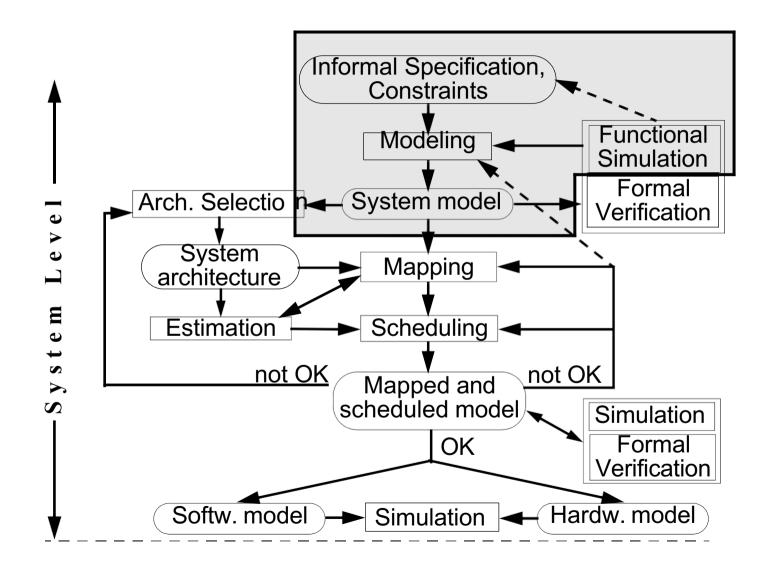

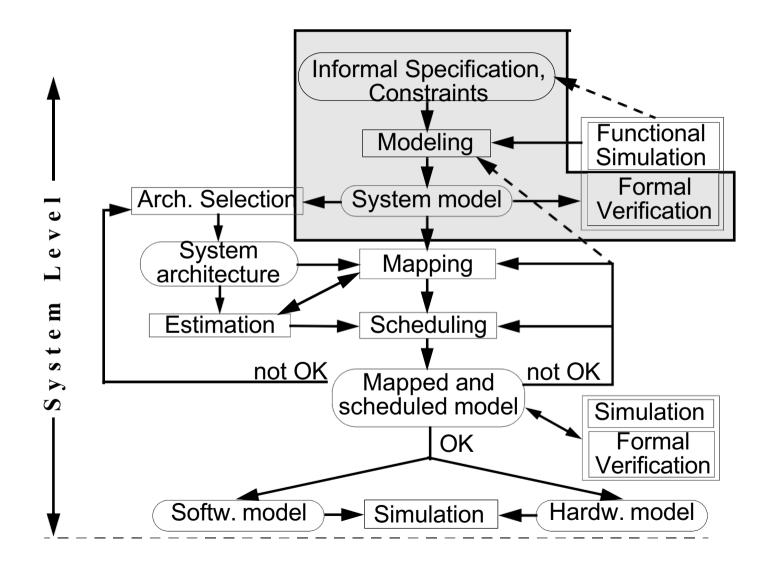

#### **The Design Flow**

#### Formal verification

It is impossible to do an exhaustive verification by simulation!

Especially for safety critical systems formal verification is needed.

#### Hardware/Software codesign

- During the mapping/scheduling step we also decide what is going to be executed on a programmable processor (software) and what is going into hardware (ASIC, FPGA).

- During the implementation phase, hardware and software components have to be developed in a coordinated way, keeping care of their consistency (hardware/software cosimulation)

## **System Level Design Flow**

This is what we are interested in, in this course!

#### **Course Topics at a Glance**

- Introduction: Embedded Systems and Their Design (just finished!)

- Models of Computation and Specification Languages

- Dataflow Models, Petri Nets, Discrete Event Models, Synchronous Finite State Machines & Synchronous Languages, Globally Asynchronous Locally Synchronous Systems, Timed Automata, Hybrid Automata.

- Architectures and Platforms for Embedded Systems Design

- General Purpose vs. Application Specific Architectures, Component and Platform-based Design, Reconfigurable Systems, Functionality Mapping.

- Real-Time Embedded Systems

- System-Level Power/Energy Optimization

## Lab Assignment 1

Modeling and simulation with System C

## Lab Assignment 2

Formal verification with UPPAAL (TDTS07 only)

## Lab Assignment 3

Design space exploration with an MPARM simulator.